VHDL-kieli FPGA-suunnittelussa/4-bittinen BCD-laskuri

Ulkoasu

Binary-coded Decimal

[muokkaa | muokkaa wikitekstiä]Binary-coded Decimal tai BCD on tapa esittää desimaaliluku bittijonona elektronisissa laitteissa. Sen sijaan, että muutettaisiin koko luku binääriksi, BCD jakaa luvun numeroihin ja muuntaa jokaisen numeron 4-bittiseksi binäärikoodiksi.

Täten, esimerkiksi, luku 345 on BCD-koodina

0011 0100 0101

Tämä on 3 numeroa pidempi kuin oikea vastaava binääri, 101011001, mutta sillä on useita etuja:

- Sitä voidaan helposti käyttää näyttöjen ohjaukseen, koska jokainen numero on koodattu erikseen.

- Se sallii jokaisen muutoksen desimaaliluvuksi; todellinen binääristä desimaaliksi muunnos on vaikeaa ja vaikeutuu aina enemmän mitä pidempi luku on.

- Skaalautuu helposti 10 tekijöillä.

BCD-koodilla on myös haittapuolensa:

- On vaikeaa toteuttaa aritmeettisia operaatioita BCD-koodilla.

- Se on hieman pidempi kuin todellinen binaari, joten se vaatii enemmän tallennustilaa.

4-bittinen BCD-laskuri

[muokkaa | muokkaa wikitekstiä]

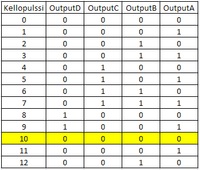

Laskee sisääntulo pulsseja nollasta yhdeksään, jonka jälkeen laskuri nollautuu ja aloittaa laskennan alusta.

Linkki videoon, joka esittää erittäin hyvin 4-bittisen BCD-laskurin toiminnan: BCD-laskuri

VHDL-toteutus, 4-Bit BCD Up Counter with Clock enable

[muokkaa | muokkaa wikitekstiä]library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Counter2_VHDL is

port( Clock: in std_logic;

Clock_enable: in std_logic;

Reset: in std_logic;

Output: out std_logic_vector(0 to 3));

end Counter2_VHDL;

architecture Behavioral of Counter2_VHDL is

signal temp: std_logic_vector(0 to 3);

begin

process(Clock,Reset)

begin

if Reset='1' then

temp <= "0000";

elsif(Clock'event and Clock='1') then

if Clock_enable='0' then

if temp="1001" then

temp<="0000";

else

temp <= temp + 1;

end if;

else

temp <= temp;

end if;

end if;

end process;

Output <= temp;

end Behavioral;