VHDL-kieli FPGA-suunnittelussa/4-bittinen ALU

4-bittinen ALU

[muokkaa | muokkaa wikitekstiä]Tietokoneen toiminta perustuu tiedolle tehtävistä laskutoimituksista ja loogisista operaatioista. Aritmeettisloogisia (ALU) yksiköitä on näitä tehtäviä varten vähintään yksi kappale jokaisen tietokoneen keskusyksikössä.

Ohessa esitellään yksinkertainen 4-bittinen ALU. Esiteltävässä ALUssa on kaksi 4-bittistä tuloa (Nibble1 ja Nibble2)ja yksi 4-bittinen lähtö (result), toimintatapa valitaan yhdellä 3- bittisellä tulolla (Operation). Piirissä on myös muistilähtö (Carry_out) ja ylivuoto bitti (Flag).

Esimerkkinä käytettävän ALUn operaatiot (Operation- tulo) ja toimintatapa

| Operation | Toimintatapa |

|---|---|

| 000 | Tulojen aritmeettinen yhteenlasku |

| 001 | Tulojen erotus, jos Nibble2- tulo on suurempi kuin Nibble1- tulo, niin ylivuoto (Flag) |

| 010 | Tulojen JA (AND) |

| 011 | Tulojen TAI (OR) |

| 100 | Tulojen eksklusiivinen TAI (XOR) |

| 101 | Tulon Nibble1 EI (NOT Nibble1) |

| 110 | Tulon Nibble2 EI (NOT Nibble2) |

| muut | Tulojen aritmeettinen erotus |

4-Bit ALU VHDL Koodi

[muokkaa | muokkaa wikitekstiä]

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity ALU_VHDL is

port( Carry_Out: out std_logic;

Flag: out std_logic;

Nibble1: in std_logic_vector(3 downto 0);

Nibble2: in std_logic_vector(3 downto 0);

Operation: in std_logic_vector(2 downto 0);

result: out std_logic_vector(3 downto 0));

end ALU_VHDL;

architecture Behavioral of ALU_VHDL is

signal temp: std_logic_vector(4 downto 0);

begin

process(Nibble1,Nibble2,Operation,temp)

begin

Flag <= '0';

case Operation is

-- Aritmeettinen summa

when "000" =>

temp <= conv_std_logic_vector((conv_integer(Nibble1) + conv_integer(Nibble2)),5);

result <= temp(3 downto 0);

Carry_Out <= temp(4);

-- Looginen erotus ja ylivuoto

when "001" =>

if Nibble1 >= Nibble2 then

result <= Nibble1 - Nibble2;

Flag <= '0';

else

result <= Nibble2 - Nibble1;

Flag <= '1';

end if;

-- AND

when "010" =>

result <= Nibble1 and Nibble2;

-- OR

when "011" =>

result <= Nibble1 or Nibble2;

-- XOR

when "100" =>

result <= Nibble1 xor Nibble2;

-- NOT Nibble1

when "101" =>

result <= not Nibble1;

-- NOT Nibble2

when "110" =>

result <= not Nibble2;

-- muut aritmeettinen erotus

when others =>

temp <= conv_std_logic_vector((conv_integer(Nibble1) + conv_integer(not Nibble2)) + 1, 5);

result <= temp(3 downto 0);

end case;

end process;

end Behavioral;

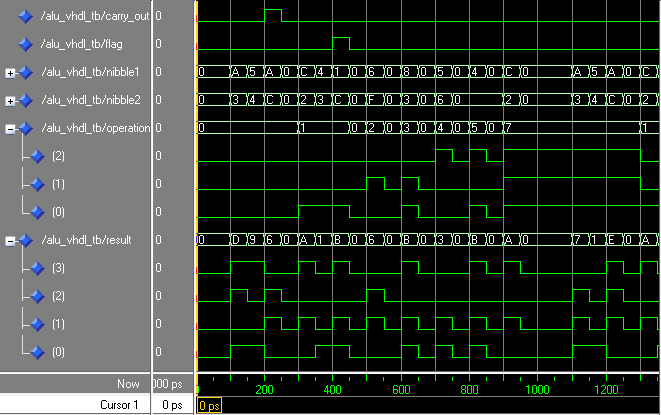

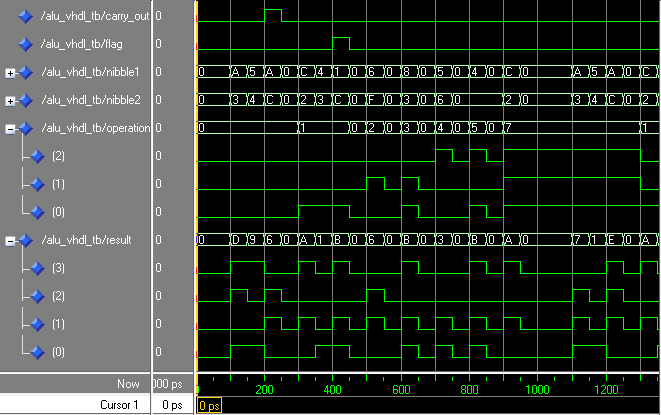

Simulaatiotulos

[muokkaa | muokkaa wikitekstiä]

Kuten simulaatiotuloksesta nähdään tulojen Operation ollessa 2 (010) ja Nibble1 on F (1111), Nibble2 on 6 (0110) on lähtö Result 6 (0110).

Operation 0 (000) tarkoittaa SUM -operaatiota ja tällöin lähtö Result = 1010 (A) SUM 1100 (C) = 0110 (6) ja Carry = 1, koska oikea tulos on 10110 (16).

Operation 2 (010) tarkoittaa AND -operaatiota ja tällöin lähtö Result = 1111 (F) AND 0110 (6) = 0110 (6).

Operation 3 (011) tarkoittaa OR -operaatiota ja tällöin lähtö Result = 1000 (8) OR 0011 (3) = 1011 (B).

Symboli

[muokkaa | muokkaa wikitekstiä]