VHDL-kieli FPGA-suunnittelussa/4-bittinen summain

Ulkoasu

4-bittinen summain

[muokkaa | muokkaa wikitekstiä]4-bittisensummaimen rakentaminen tapahtuu ketjuttamalla neljä kokonaissummainta yhteen viemällä kokonaissummainen Cout toisen summaimen Cin nastaan, kuten alhaisessa kuvassa tehdään.

Toiminta esimerkki

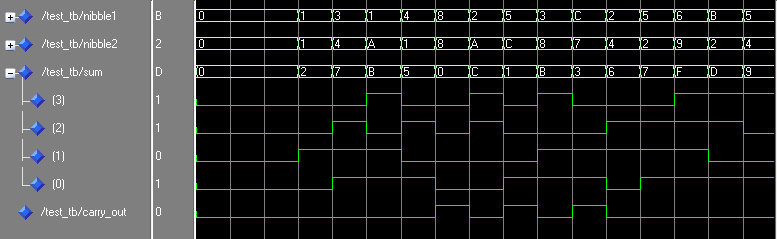

[muokkaa | muokkaa wikitekstiä]Jos syötämme ylhäällä olevaan summaimen lähtöihin alhaalla olevasta simulaatio esimerkistä heksaluvut 2 ja A eli 0010 ja 1010 summaimen tuloista tulee logiikka piirien sääntöjen mukaisesti heksaluku C 1100.

VHDL koodi

[muokkaa | muokkaa wikitekstiä]library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Adder is

port( Nibble1, Nibble2: in std_logic_vector(3 downto 0);

Sum: out std_logic_vector(3 downto 0);

Carry_out: out std_logic);

end Adder;

architecture Behavioral of Adder is

signal temp: std_logic_vector(4 downto 0);

begin

temp <= conv_std_logic_vector( (conv_integer(Nibble1) + conv_integer(Nibble2)),5);

Sum <= temp(3 downto 0);

Carry_out <= temp(4);

end Behavioral;

Simulaatiotulos

[muokkaa | muokkaa wikitekstiä]Katso myös

[muokkaa | muokkaa wikitekstiä]Lähteet

[muokkaa | muokkaa wikitekstiä]- Seppo Haltsonen, Jaakko Levomäki, Esko T. Rautanen: Digitaalitekniikka. Edita, 2004. ISBN 951-37-3886-8.