VHDL-kieli FPGA-suunnittelussa/Prioriteettienkooderi

Ulkoasu

Prioriteettienkooderi

[muokkaa | muokkaa wikitekstiä]Prioriteettienkooderi asettaa datassa olevat tärkeämmät bitit etusijalle ja ohittaa alemmat signaalit kokonaan saadessaan ylimmän tason signaalin. Eli In bitin ollessa '1' enkooderi ohittaa kaikki In-1 bitit. Esimerkissä neljä kahteen enkooderi, jossa ylimmän tason bitti on I3 ja merkityksettömin on I0, lisäksi D ilmaisee sen että onko datassa lainkaan aktiivista signaalia.

| I3 | I2 | I1 | I0 | O1 | O0 | D |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | d | 0 | 1 | 1 |

| 0 | 1 | d | d | 1 | 0 | 1 |

| 1 | d | d | d | 1 | 1 | 1 |

4 to 2 -enkooderi

VHDL ja logiikkakaavio

[muokkaa | muokkaa wikitekstiä]library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Priority_Encoder_VHDL is

port ( Sel : in std_logic_vector(3 downto 0);

encoded_data : out std_logic_vector(1 downto 0);

D : out std_logic);

end Priority_Encoder_VHDL;

architecture Beh of Priority_Encoder_VHDL is

begin

encoded_data <= "11" when Sel(3)='1' else

"10" when Sel(2)='1' else

"01" when Sel(1)='1' else

"00";

D <= '0' when Sel="0000" else '1';

end Beh;

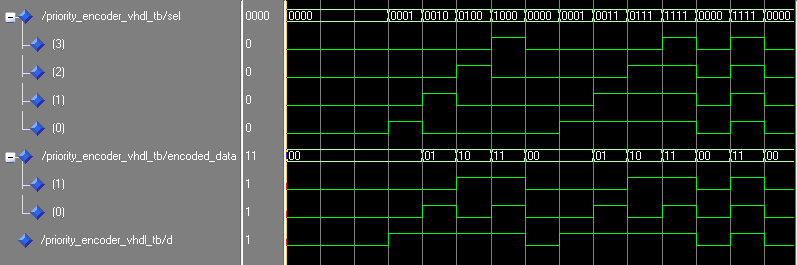

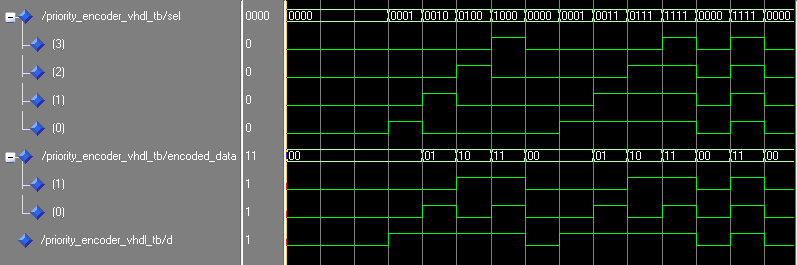

Simulaatiotulos

[muokkaa | muokkaa wikitekstiä]