VHDL-kieli FPGA-suunnittelussa/T-kiikku

Ulkoasu

T-kiikku

[muokkaa | muokkaa wikitekstiä]

Jos T-tulon arvo on 1, kiikun tila komplementoituu kellon aktiivisella reunalla. Jos T-tulon arvo on 0, kiikun tila säilyy kellon aktiivisella reunalla. Tämä käyttäytymismalli on kuvattuna tässä yhtälössä:

- (tai vastaavasti ilman XOR-operaattoria: )

ja kuvattuna totuustaulussa:

| Kommentti | |||

|---|---|---|---|

| 0 | 0 | 0 | ei muutosta |

| 0 | 1 | 1 | ei muutosta |

| 1 | 0 | 1 | komplementointi |

| 1 | 1 | 0 | komplementointi |

T-kiikku on mahdollista toteuttaa myös käyttämällä JK-kiikkua (J- ja K-tulot kytkemällä yhteen, käyttäytyy T-tulon tavoin) tai D- kiikkua käyttämällä (T-tulo ja edellinen Q-tulo liitetään D-tuloon XOR-portin kautta).

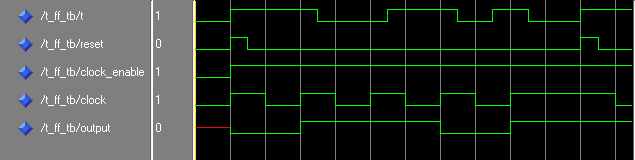

T-kiikun VHDL toteutus

[muokkaa | muokkaa wikitekstiä]

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity T_FF_VHDL is

port( T: in std_logic;

Reset: in std_logic;

Clock_enable: in std_logic;

Clock: in std_logic;

Output: out std_logic);

end T_FF_VHDL;

architecture Behavioral of T_FF_VHDL is

signal temp: std_logic;

begin

process (Clock)

begin

if Clock'event and Clock='1' then

if Reset='1' then

temp <= '0';

elsif Clock_enable ='1' then

if T='0' then

temp <= temp;

elsif T='1' then

temp <= not (temp);

end if;

end if;

end if;

end process;

Output <= temp;

end Behavioral;